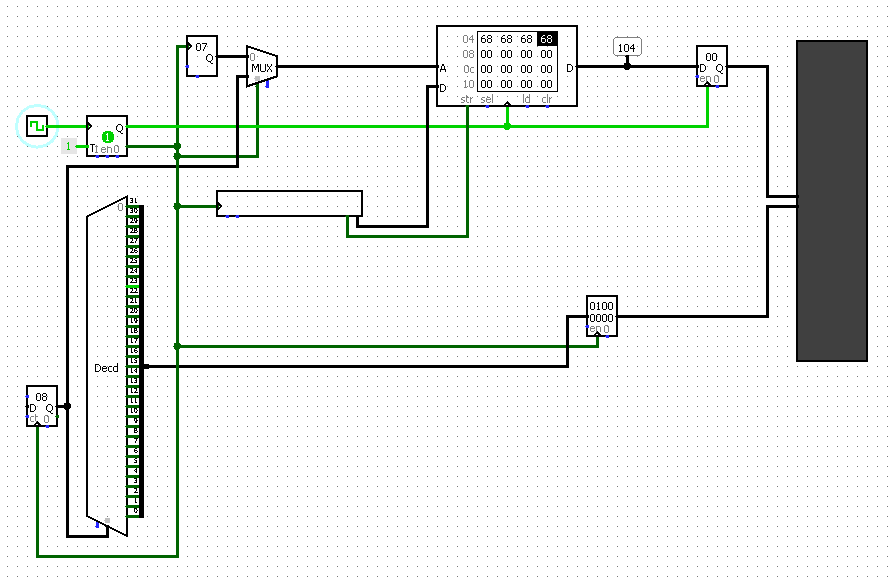

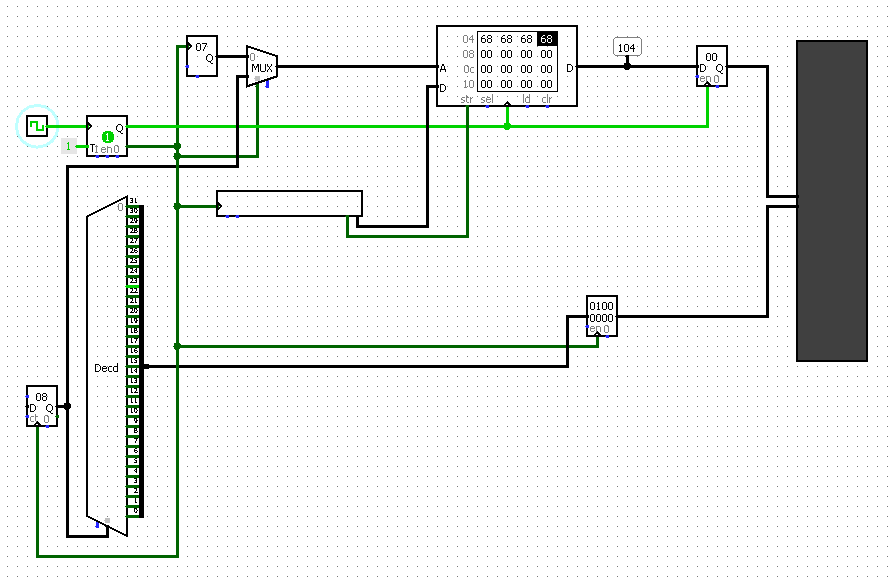

Поставленная задача: создать схему устройства, реализующего совместный доступ устройств ввода и вывода к ОЗУ. Разрядность адреса ОЗУ — 5 битов, разрядность данных — 7 битов. По нечётным тактам в ячейку ОЗУ со случайным адресом (сгенерированным генератором случайных чисел) записывается ASCII код символа из буфера компонента «Клавиатура», причём если буфер пуст (на выходе компонента - значение «0»), то запись не происходит. По чётным тактам происходит вывод содержимого ОЗУ на светодиодную матрицу размером 7x32 с помощью развёртки, то есть каждый чётный такт — следующая строка точек.

-не полностью реализована(

проверка на четность/нечетность и последовательный вывод в связи с этим не работает корректно)(реализована в программе Logisim)

подскажите пожалуйста, в чем ошибки реализации? или посоветуйте возможное альтернативное схемное решение

представляю файл:

ус-во.zip (1,67К)

ус-во.zip (1,67К)

Помощь

Помощь